臺大團隊2017年ACM ISPD奪銀 居全球總冠軍

臺大電機研發團隊勇奪2017年ACM ISPD國際積體電路實體設計研發競賽第二名,冠軍及總獲獎次數居世界各單位之冠。

臺大電子與電機研究所於電子設計自動化領域最重要國際競賽再獲佳績!今年於美國奧勒岡州波特蘭市 (Portland) 舉辦的「ACM 國際積體電路實體設計會議」 (ACM International Symposium on Physical Design, ISPD) 公布為期三個多月的「ACM ISPD考慮時序的現場可程式邏輯陣列擺置研發競賽」(ACM ISPD Clock-Aware FPGA Placement Contest)最終結果,由臺大電機系與電子所張耀文教授 (副教務長)、郭斯彥教授 (電機資訊學院前院長) 及電子所學生郭質、黃朝琴、陳士鈞、蔣君涵所共同研發的現場可程式陣列擺置器NTUfplace獲得了第二名的榮耀! 「ACM ISPD 國際積體電路實體設計研發競賽」是由全球研究計算機科學的權威學會ACM (Association for Computing Machinery) 所舉辦。為歷史最悠久和最著名的電子設計自動化研發競賽,曾被電機資訊領域最重要國際媒體 EE Times 的資深技術編輯 R. Colin Johnson (2010 京都賞 [Kyoto Prize in Journalism] 得主) 譽為「地表最優秀工程人才競技場」 (“The best engineering minds on the planet compete each year in the ACM’s ISPD design contest, which was won this year by the National Taiwan University” (4/6/2015, EE Times)。在13屆的競賽中,張耀文教授研發團隊參賽11次,共計獲得第一名三次,和第二、第三和第四名各兩次。冠軍數和總獲獎數皆居世界各單位之首 (德州大學奧斯汀校區Univ. of Texas at Austin和密西根大學安那堡校區Univ. of Michigan at Ann Arbor居次),大幅提升臺大在此領域的領導地位。臺灣和張耀文教授研發團隊在電子設計自動化領域的重要國際地位,曾獲 EE Times 報導: “Taiwan''s success so far has been in large part due to electronic design automation (EDA) expertise, where has only been outperformed by the U.S. for the last five years… Yao-Wen Chang is typical at NTU, a microelectronics pioneer in EDA, due to receive four separate awards at DAC 2013’s 50th anniversary celebration next month, all related to his unstoppable stream of DAC research papers presenting deep insights into EDA.” (5/15/2013, R. Colin Johnson)

此競賽於2005年首辦,至今年為第13屆,每年12月委由業界一流公司 (今年為賽靈思公司 Xilinx, Inc.) 公布研發競賽題目,3月繳交研發成果和軟體系統,由業界公司負責提供測試電路,並測試參賽隊伍所繳交的軟體系統,最後於4月假年度「ACM 國際積體電路實體設計會議」 (ACM ISPD) 公佈競賽結果 (會議網站為www.ispd.cc)。每年競賽題目皆為當今產學界研究積體電路實體設計流程中的重要議題,如擺置 (Placement) 競賽、全域繞線 (Global Routing) 競賽、時脈網路合成 (Clock Network Synthesis) 競賽以及元件尺寸最佳化 (Gate Sizing) 競賽,皆吸引世界各地的頂尖研究團隊參賽,以期對目前產學界遇到最棘手的實體設計問題研發出解決方案。歷年來,此競賽已成為電子設計自動化領域的年度盛事,每年競賽結果皆吸引產學界高度關注,並獲半導體工業最重要的專業媒體「電子時報」 (EE Times) 的報導。(參見今年報導EE Times: “ISPD Predicts Chip Futures,” by R. Colin Johnson。)

今年的競賽題目為開發一個考慮時序的現場可程式邏輯陣列擺置系統,旨在將給定的數百萬電路元件擺置於現場可程式邏輯陣列晶片上的最佳位置,以求電路元件間的總連線長度最短、電路速度最快並符合指定的時序條件,並滿足業界晶片設計的低功耗技術考量,此問題為當代積體電路設計自動化所面臨的最關鍵挑戰之一。參賽者所開發的軟體系統必須成功擺置由 Xilinx 所提供的13個實際業界電路和5個特殊測試電路,同時也必須能達到短線長、符合時序條件以及快速完成擺置的目標,以符合當今日趨複雜的電路系統設計需求。競賽結果由Xilinx 所研發的套裝軟體 (Vivado Design Suite) 進行評分,分別對13組設計做排名後,平均排名總和較小的隊伍獲勝。本屆競賽競爭激烈,參賽隊伍主要來自亞洲、北美洲、南美洲和歐洲的研究團隊,不僅涵蓋各地知名學府,及台灣的臺大、交大等頂尖學校參與。

此次競賽結果臺大團隊所研發擺置器NTUfplace,獲得第二名,略次於德州大學奧斯汀校區團隊,第三名由香港中文大學團隊獲得。臺大為該競賽冠軍及總獲獎次數全球之冠,此為臺大贏得了極高的學術聲望及國際能見度。值得一提的是,電路擺置 (placement) 的技術為當今積體電路設計自動化領域最受注目的主題之一,此使得三大頂尖電子設計自動化國際會議 (ACM ISPD、ACM/IEEE DAC及IEEE/ACM ICCAD) 皆於近年舉辦國際擺置研發競賽,而本校電子所和電機系張耀文教授研究團隊為全球唯一於此三大頂尖國際競賽皆曾獲冠軍的團隊,而該團隊也在近十一年來每年於此三大頂尖會議發表最多論文者,今年六月更獲得 DAC的最佳論文獎 (約 700 篇交件論文中第一名),為該會 54 年來台灣的第二個最佳論文獎 (第一次獲於1988年),足見近年來臺大在電子設計自動化領域的領導地位。

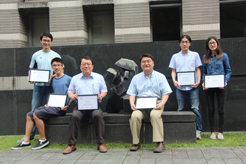

圖一: NTUfplace研發團隊成員(左起: 黃朝琴、陳士鈞、郭斯彥教授、張耀文教授、郭質、蔣君涵)

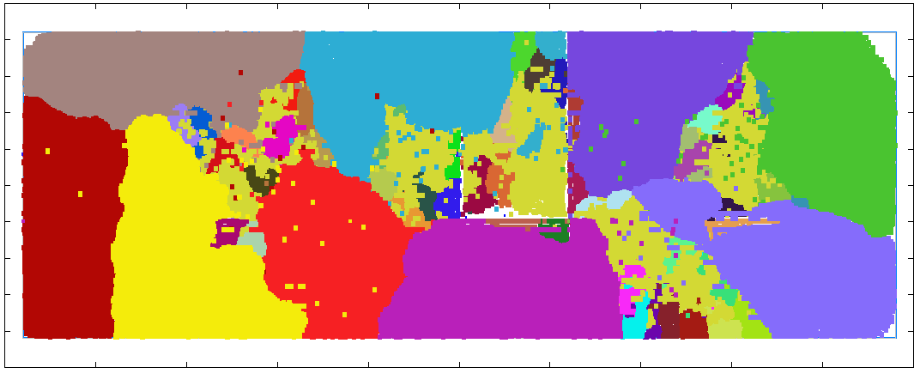

圖二: 競賽第二名獎牌

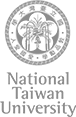

圖三: 測試電路擺置結果,內含九十餘萬個電路元件(各個顏色的小點)和九十餘萬條訊號線(未顯示於圖中),各顏色表示不同時序之電路元件。