臺大研究成果系列報導 劉致為教授90nm / 5nm / 2nm半導體技術節點及基礎物理之研究

數位化改變了人們的生活方式,現今生活中的科技裝置,大到汽車小如手機,無不以半導體晶片為重要核心。隨著科技不斷的進步,5G世代的來臨,AI智慧、物聯網及行動智慧裝置的普及,均賴以先進半導體晶片的性能不斷提高;研究團隊對於製程技術努力研發,才能使半導體製程技術大幅提升元件性能,開發更具競爭力的晶片產品。

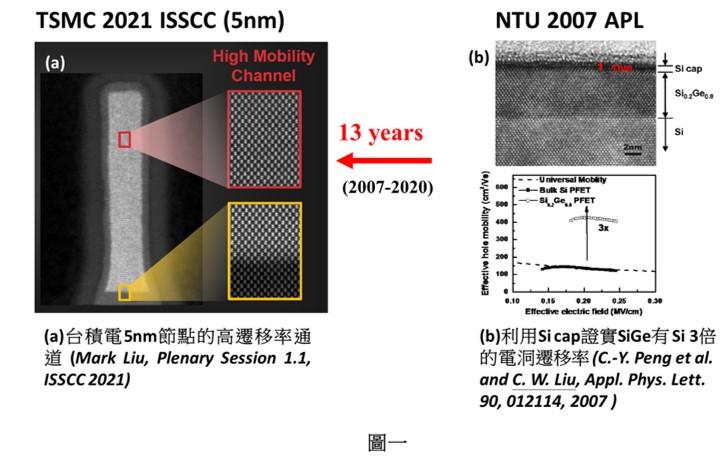

過去在平面電晶體技術發展中,有二項重要突破 (1)Strained Si、(2)high k/metal gate。劉教授早期在臺大主要的研究是Strained Si,該理論早已知,技術則是由Bell labs的Eugen Fitzgerald博士(現MIT教授)及謝亞弘博士(現UCLA教授),用Molecular Beam Epitaxy證實,並在90nm技術節點開始量產;之後平面電晶體由胡正明院士團隊提出的FinFET結構所取代,於22奈米技術節點(Intel)及16奈米技術節點(台積電)被業界採用,成為現今先進半導體的主流。眾所期待元件擁有高遷移率通道(high mobility channel),台積電在5奈米技術節點終於量產,在IEDM 2020宣佈,圖一(a)為台積電於2021年舉辦的國際固態電路研討會(ISSCC)中所發表之高遷移率通道結構,是採用劉教授研究團隊於2007年發表的Si cap on SiGe通道之元件結構(圖一(b)APL 2007)。

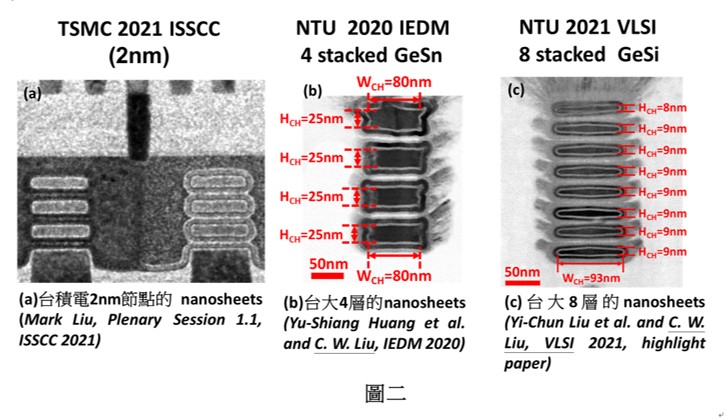

三星與台積電兩大晶圓代工巨頭先後宣布3奈米技術節點(Samsung)及2奈米技術節點(tsmc),電晶體結構將採用gate-all-around (GAA) 的nanosheet結構,這使得原本為半導體明日之星的GAA技術,瞬間大放異彩,眾研究團隊及學者無不凝神注視其發展,劉教授的研究團隊在2007年開始研究GAA技術,圖二(a)為台積電於ISSCC 2021中所發表之研究成果,與劉教授團隊研究成果之TEM照片做對照,如圖二所示。台積電(圖二(a))展示出3層的nanosheets,而劉教授團隊已做到4層(圖二(b))甚至是8層(圖二(c)),而最新研究成果16層的nanosheets預計將投稿IEDM 2021,目前臺大乃是業界以外,唯一能研發多層GAA nanosheets的大學;FinFET已從16nm、10nm、7nm、5nm、3nm共發展了5代,期待nanosheets從2nm可以走到1nm以下節點。劉教授於基礎科學上亦有所突破:⍺-Sn在過去幾十年一直被認為是semi metal,而劉教授研究團隊理論證明應為zero bandgap semiconductor,而且擁有高濃度Sn的GeSn亦是如此,為研發GeSn元件的重要基礎理論。劉教授團隊製作世界遷移率最高的strained Si,1,600,000 cm2/Vs,由諾貝爾獎得主崔琦教授驗証(2009,APL),現已增加到2,400,000 cm2/Vs,仍為世界記錄。用於研究valleytronics及many particle effects,希望再增強電子元件的率能。

劉致為教授在此感謝研究生們在無塵室的辛苦及創造的智慧、指導教授Jim Sturm(Princeton)對其犯錯的容忍和創意的鼓勵、胡正明院士十餘年的指導與合作以及馬佐平院士多年來的指導,和崔琦院士在high mobility Si研究的支持。